SPMI Protocol Analyzer(PGY-SPMI-EX-PD) is the Protocol Analyzer with multiple features to capture and debug communication between host and design under test. SPMI (System Power Management Interface) is a MIPI (Mobile Industry Processor Interface) standard with 2-wire synchronous serial, bidirectional interface that connects the integrated Power Controller(PC) of a System on- Chip (SoC) processor system with one or more Power Management Integrated Circuits (PMIC) voltage regulation systems.

[Datasheet Download]

PGY-SPMI-EX-PD is the leading instrument that enables the design and test engineers to test the SPMI designs for its specifications by configuring PGY-SPMI-EX-ED as master/slave, generating SPMI traffic with time variation and error injection capability and decoding SPMI Protocol packets.

Features

- Supports SPMI v 1.0/ 2.0 specifications

- Ability to configure it as Master or Slave

- Supports Sole Master feature

- Supports Request Capable Slave (RCS) feature

- Supports the complex BUS arbitration process

- Generate different SPMI Packets

- Error injection such as parity error, ACK/NACK error and Skip SSC error

- Variable SPMI data speeds (32kHz – 26Mhz1), Voltage drive levels (1.2 or 1.8) and Duty Cycle (25%,50% and 75%).

- Simultaneously generate SPMI traffic and Protocol decode of the Bus

- Continuous streaming of protocol data to HDD/SSD

- Timing diagram of Protocol decoded bus

- Listing view of Protocol activity

- Error Analysis in Protocol decoded data

- Ability to write exerciser script to combine multiple data frame generation at different data speeds

- USB2/3 host computer interface

- API support for automation in Python and C++

- Flexibility to upgrade to the unit for evolving SPMI Specification

- Optional Protocol Implementation Compliance Statement (PICS) support scripts

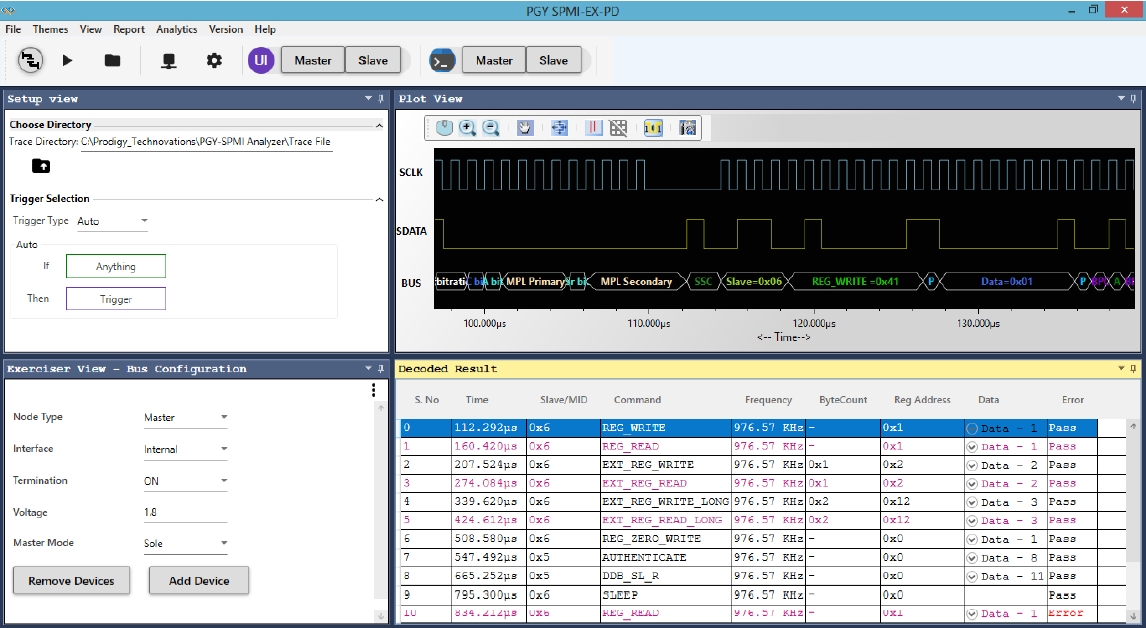

Comprehensive Protocol Analysis using Multi-View

Multidomain View provides the complete view of SPMI Protocol activity in single GUI. User can easily setup the analyzer to generate SPMI traffic using a GUI or script. User can set different trigger conditions from the setup menu to capture Protocol activity at specific event and decode the transition between Master and Slave. The decoded results can be viewed in timing diagram and Protocol listing window with autocorrelation. This comprehensive view of information makes it industry best, offering an easy to use solution to debug the SPMI protocol activity. Continuous streaming protocol activity to host system HDD/SSD ensures seamless roll mode operation without the need to recapture data when DUT/s are set to different states thereby saving test times.

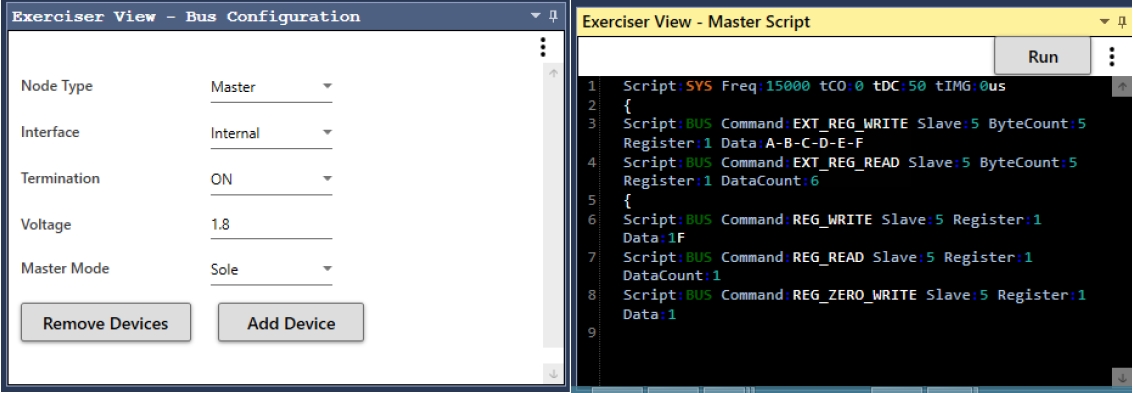

Exerciser

PGY-SPMI-EX-PD supports SPMI traffic generation using GUI and Script. User can generate simple traffic generation using the GUI to test the DUT. Script based GUI provides flexibility to emulate the complete expected traffic in real world including error injections. In this sample script user can generate SPMI traffic as below.

Script line #3: Ext Reg Write to the slave with USID 05

Script line #4: Ext Reg Read to the slave with USID 05

Script line #6: Reg Write to the slave with USID 05

Script line #7: Reg Read to the slave with USID 05

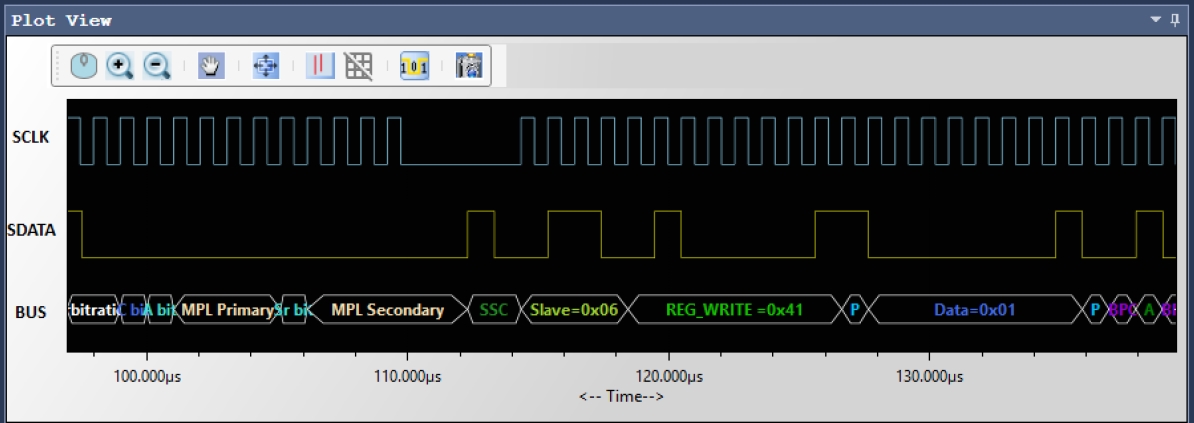

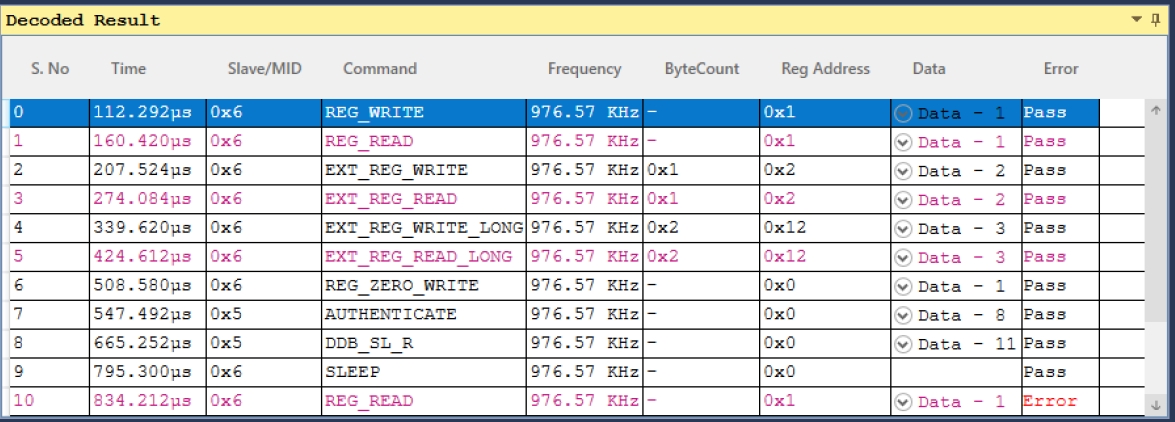

Timing Diagram and Protocol Listing View

Timing view provides the plot of SCL and SDA signals with bus diagram. Overlaying of Protocol bits on the digital timing waveform will help easy debugging of Protocol decoded data. Cursor and Zoom features will make it convenient to analyze Protocol in timing diagram for any timing errors.

Protocol window provides the decoded packet information in each state and all packet details. Selected frame in Protocol listing window will be auto correlated in timing view to view the timing information of the packet.

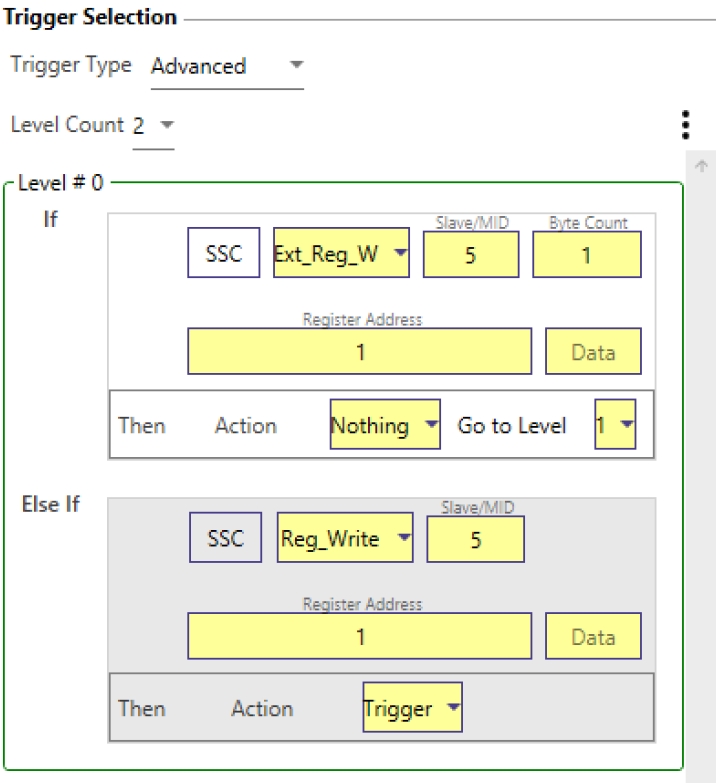

Powerful Trigger Capabilities

PGY-SPMI-EX-PD supports simple trigger capabilities. Analyzer can trigger on any of the Protocol packets such as Reg Write, SLEEP or WAKE UP. Advanced Trigger provides the flexibility to monitor Multiple trigger conditions and can set multiple state trigger machine. User can initiate a timer and trigger on set timer values.

Protocol Implementation Compliance Statement (PICS) test scripts

Optional PICS capability enables designers to test their designs for compliance as per the PICS requirement of SPMI specifications. The software provides the flexibility for designers to select 1/few/All test cases and run them automatically using this PICS feature of the product.

Supports 200+ test Id scripts

The tests are run as per defined steps and gives a PASS/FAIL verdict for each test. This is a critical step to ensure in-house compliance testing is enabled and help the design teams to ensure their implementation is as per SPMI standards. The key outcome of this is to shorten the time to market of the products with the assurance that the design meets the SPMI PICS implementation.

A detailed report captures the PICS results with the PASS/FAIL verdict

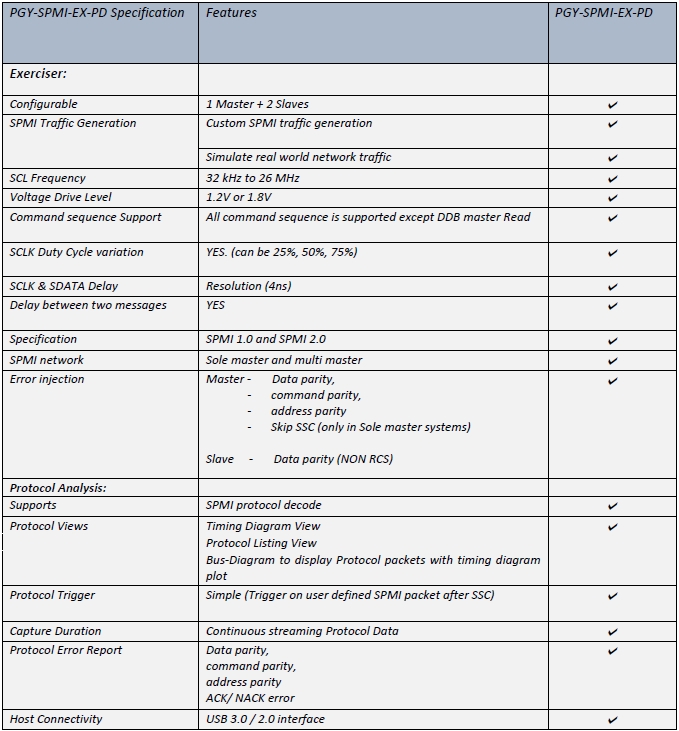

SPMI Specifications